# In-Circuit Debug Techniques for System Designs Utilizing FPGAs

### July 23, 2003

presented by:

## **Brad Frieden**

© Copyright 2003 Agilent Technologies, Inc.

Welcome.

#### Agenda

Welcome to Agilent's eSeminar on debug methodologies for FPGA-based systems. Today, we'll look at the nature of such systems and how that presents debug challenges. Next, we'll consider the ways that one can get access to internal FPGA signals as well as other system signals. Then we'll spend most of our time looking at real-life design examples and how designers debugged problems in those systems. Based on what we learn from these cases, a number of helpful approaches and tips become evident and we will discuss those. Finally, we'll also consider options related to high-speed I/O.

Let's begin by considering some of the unique challenges related to FPGA system debug.

When you look to the nature of the F P G A systems, there are a number of factors that can make in circuit debug a challenge. First of all a good portion of the innovation is what is placed inside the FPGA, so the FPGA ends up becoming a focus of the debug and validation effort.

It is often very important to be able to see inside the FPGA but often that is easier said than done because the external pins are often not available for debug or only a limited number are available.

EPA tools work very well for synchronous designs but asynchronous situations, like crossing time domains can become quite tricky.

With some of the latest FPGAs is it is now possible to include large IP blocks such as microprocessors. Some of the IP, the hard cores, where Xilinx provides a black box functionality, does not allow you to look inside, thus limiting your visibility. With soft cores that are synthesized from R T L code, it is possible to look inside.

The size of available FPGAs is getting larger and the possible speeds are increasing. Even though the devices are larger, the designs are now larger too and can still find yourself pin limited.

This increasing complexity presents some new challenges for debug and system integration.

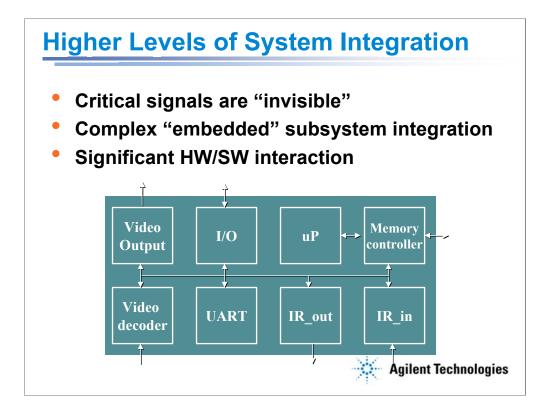

Critical signals are buried deep and not naturally visible.

Entire subsystems are internal to the FPGA, limiting or complicating system integration & debug.

System complexity increases dramatically; integration challenges are higher than ever.

When it comes to Fast I/Os, especially those running at GHz rates, PC board traces are essentially acting as transmission lines. Part of the system design involving FPGAs with fast I/Os is the careful design of the signal path.

Lets now turn to general system debug and the main ways it is possible to see internal nodes inside an F PGA

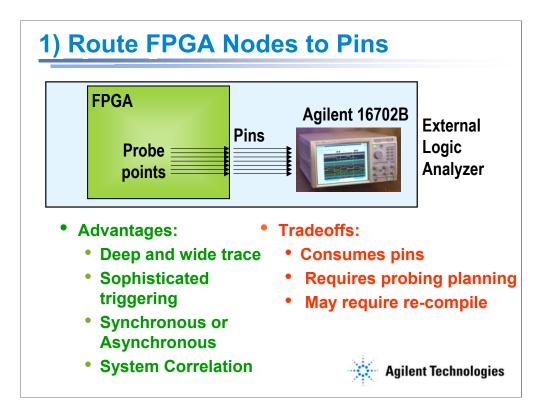

The first approach is pretty basic—just route out the nodes of interest directly to external pins on the FPGA and look at them with a logic analyzer. With this method come a number of advantages surrounding the debug features of an external logic analyzer such as deep memory and sequence triggering. It's also very straightforward to correlate internal FPGA signals with other signals captured from the target system.

Of course, the big issue can be how many pins are available for this. Certainly, this approach also carries with it a moderate investment. However, the logic analyzer is used for many other general purpose applications.

It's best to determine early in the development process how many pins you want to dedicate to debug.

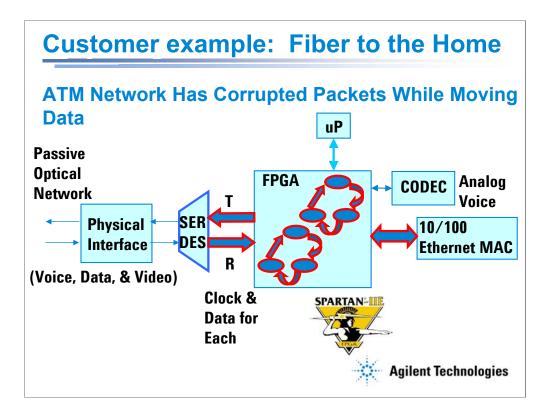

Let's look at an engineering example where this approach was used. Here a designer was experiences problem with a Fiber to the Home ATM Network that would reside at the customer location. This was the part of a system which connected to a passive optical network and then pulled out voice, data, and video into standard formats for use at the customer site. The system was experiencing corrupted packets while moving data. Some of the system characteristics were:

ATM network bringing fiber into a home and offering voice, video and data capability

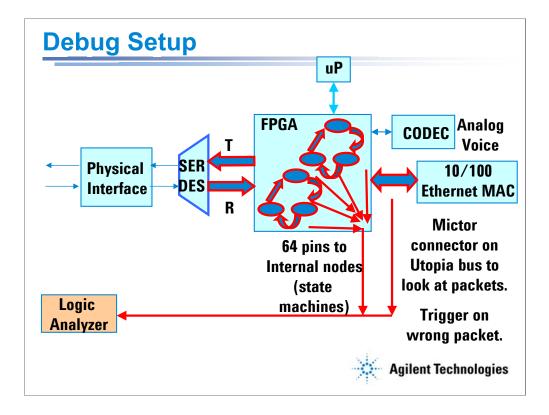

The FPGA is in the data path and takes in raw data from fiber optic clock and data recovery circuits. The FPGA served as a packet processing engine. Multiple state machines, triggered by cells coming through, would look at cell headers and determine what kind of service was being processed. They would then perform decoding, buffering and formatting operations. The state machines had to be "perfectly timed".

Puts out Ethernet frames to the 10/100 Ethernet parts

Are a number of Utopia buses all over and "sort of Utopia" buses for proprietary chip to chip communications

In this situation, the designer chose a large FPGA, many times that needed for the final design, for use in developing the system on a prototyping board. This prototyping board had the things they anticipated for the final design, all the optical circuitry, a microprocessor, and Ethernet.

The strategy was to get Mictor connectors on the board from the get go, and they dedicated 64 pins on the FPGA for debug. He placed a Mictor connector on a utopia bus in order to view traffic.

Key to the approach is triggering at a high packet level and then viewing the condition of multiple state machines inside the FPGA via numerous debug pins.

Their goal was to trigger the logic analyzer from the utopia bus, where they were seeing wrong packets, and then look at the exact condition of the state machines to try and sort out what was going wrong.

| Analyzer <a> - 167MHz State/667MHz Timing 2M Sample A</a>        |                    |

|------------------------------------------------------------------|--------------------|

| File Window Edit Options Clear                                   | Help               |

|                                                                  |                    |

| Sampling Format Trigger Symbol                                   |                    |

| Trigger Functions Settings Overview Default Storing Status Save  | Recall             |

| General State, Telecom State, InfiniBand St Trigger function lib | raries             |

| Find InfiniBand Packet<br>Find Serial ATA Packet                 | CADDR<br>TADDR<br> |

|                                                                  |                    |

| Trigger Sequence 1 FIND PACKET                                   |                    |

| 0n bus RX UTOPIA                                                 |                    |

| If VP 0x50 occurs once                                           |                    |

| then Trigger and fill memory Help                                |                    |

| Cherr Hitzber dire ittt memory lieth                             |                    |

|                                                                  |                    |

| Help Close                                                       | 1                  |

The logic analyzer allowed the designer to set up a specific Utopia bus packet condition to trigger on.

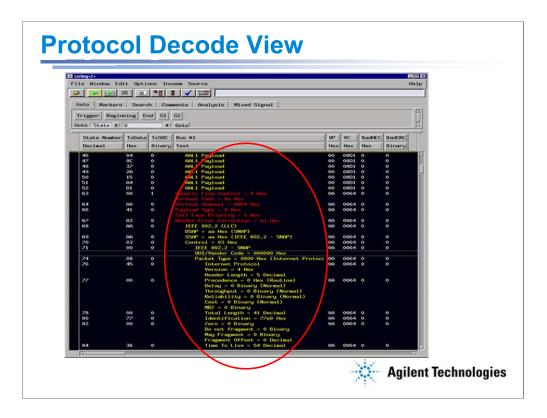

Now it was possible to see the traffic on the Utopia bus, not just in low level Hex values, but also at a protocol level.

He watched the utopia bus at a packet level with the Datacom Tool Set in the logic analyzer. He was able to see and trigger on corrupted packets as hoped.

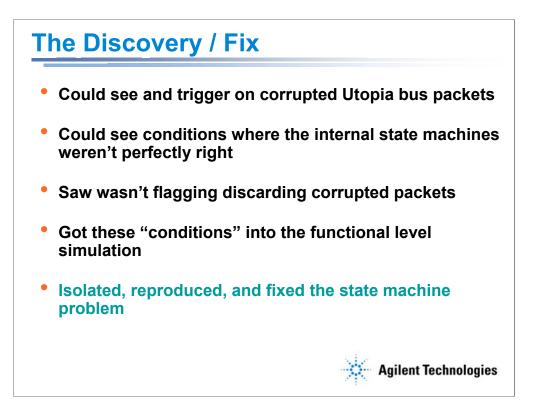

As he looked at the state machine activity inside the FPGA, immediately before the corrupted packet, he could seek the exact condition where one of the state machines wasn't perfectly right. In fact, corrupted packets were supposed to be detected and flagged as something to be discarded, but that wasn't happening. So it was normal that the memory might overflow in heavy traffic situations and packets get corrupted, but it was unacceptable to fail to flag the errors.

Key to the process was getting these conditions into the functional level simulation. Then there were able to isolate, reproduce in simulation, and then fix in simulation, the state machine problem.

A few takeaways from this example:

The engineer really valued having a lot of debug pins and chose the FPGA accordingly.

It was critical of First probe the data bus and then see the condition of the internal state machines. The engineer pointed out that it was a very difficult to stimulate traffic, and by identifying specific traffic conditions that caused problems, he was able to extend the coverage of the test bench in simulation.

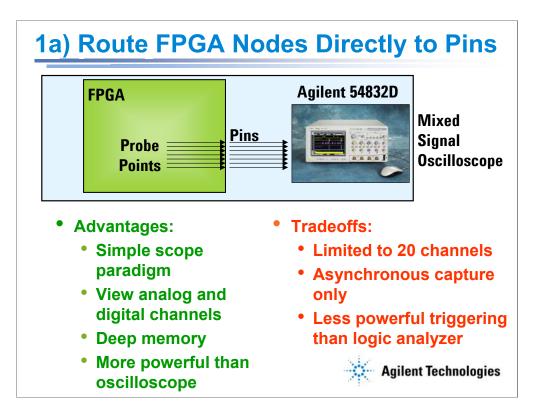

One variation to this first approach is to use a Mixed Signal Oscilloscope, or MSO to monitor signals on FPGA debug pins or other pins of the FPGA instead of using a logic analyzer.

An MSO can serve as a basic, easy to use tool for observing FPGA activity as well as observing signals on the FPGA boundary as the FPGA interfaces to other parts of a system. Because an MSO offers 4 analog channels plus another 16 digital channels with deep memory capture, there's the opportunity to observe operations like state machine activity, with some hope of triggering on a symptom of a problem, while looking backward in time to find a root cause of a problem. Depending on how difficult the debug situation, the MSO can serve as a starting point, and a logic analyzer can be brought in when more complex triggering, greater channels, or other logic analyzer capabilities are needed.

With the analog channels of an MSO or a standard oscilloscope, one has high resolution to view signal characteristics at the FPGA boundary. Such signals must meet specifications to interface to the rest of the system. An oscilloscope can make detailed timing measurements and view signal integrity characteristics of signals present. Some of these scope capabilities are less pertinent if trying to observe activity "inside" the FPGA via debug pins. Because of the routing delays to debug pins, channel to channel skew is introduced which obscures the actual timing present inside the FPGA

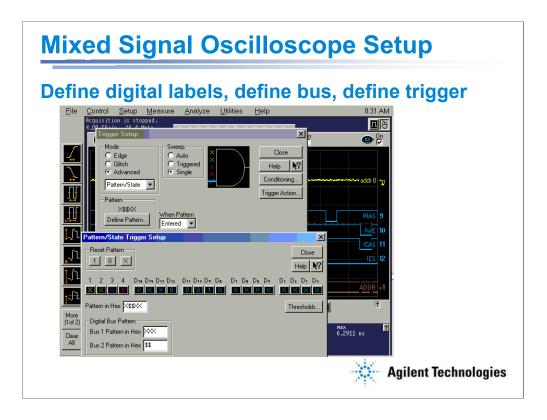

In many digital applications today, it has become important to be able to look at digital signals of interest under very specific target conditions, such as a memory write in SDRAM. Traditional oscilloscopes, with only 2 or 4 analog input channels, aren't able to trigger on the more complex control lines that define such conditions.

Now, with Mixed Signal Oscilloscope, it's very simple to label bits of interest, including multi-signal buses, and then define a trigger condition of interest.

Here, the MSO triggers when RAS is high, CAS low, Write Enable low, Chip Select low, and on the rising edge of clock.

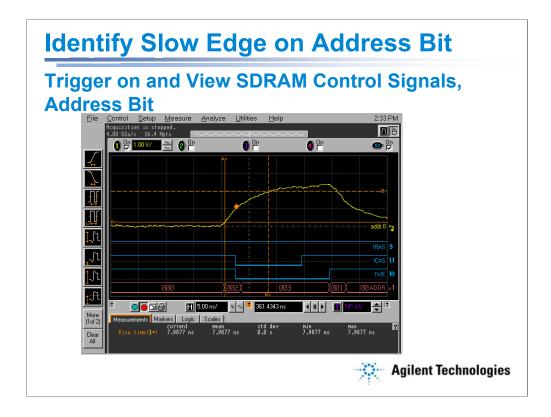

Notice that the address does not cleanly change from 000 to 003 and back, but instead takes a while to finally reach a 003 value. Having triggered on a memory write, and then scrolled through the trace to this problem point, an analog channel was then used to view the problem bit to look for the root cause of the problem. It wasn't skew or ground bounce, but rather, it was a slow edge, perhaps from a weak driver.

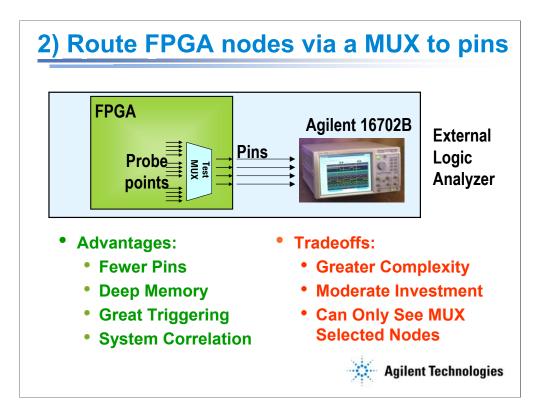

The second approach is similar to the first except that internal nodes are routed to a MUX and fewer pins are dedicated to debug. The disadvantage here is managing the MUX process and you can't see all the signals at once.

Our research shows that many designers build in a test MUX that allows a customer to select a single group of signals to bring out to the pins at a single time. This technique minimizes the number of pins dedicated for debug. Typcial pin count for debug is in the range of 8 to 32 pins while internal nodes feeding the MUX is typically in the order of 32 to a hundred channels. When the customer finishes debug, the text MUX circuitry and pins for debug remain in the design. Taking them out would change the design characteristics and require a new round of debug.

This approach also has the variation of using an MSO or traditional scope to observe signals.

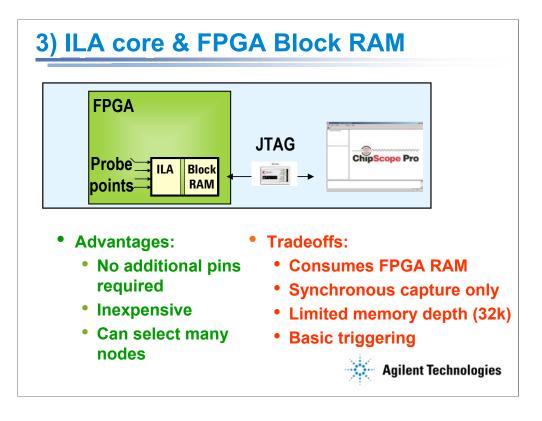

Several vendors offer options to embed logic analyzer cores inside their FPGAs. For example, Xilinx has Integrated Logic Analyzer (ILA) cores including internal block RAM to store signals. Nodes of interest are selected, traces captured, and then output via JTAG to their ChipScope software.

One big advantage here is that no FPGA pins are required beyond the JTAG connection. This is particularly useful for designs that do not have pins available for debug. It's also an inexpensive solution.

There are a number of tradeoffs. These include limited memory, the consumption of important FPGA memory, and limited triggering. As with all cores, inclusion of a logic analyzer core will have an impact on the design itself. For this reason, many engineers prefer to leave the core in the FPGA even after the design is debugged.

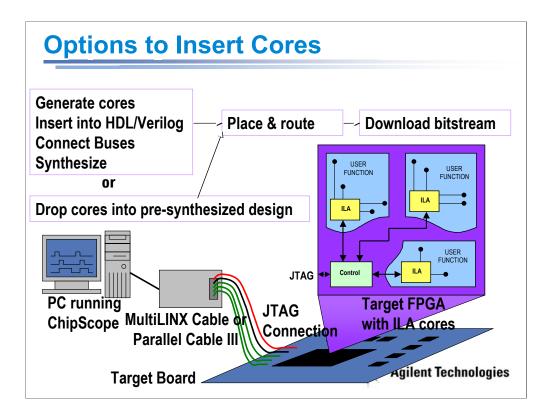

There are a couple of ways to insert ILA blocks into a design. The first involves inserting them at the verilog level synthesizing the design and then doing a place-and-route. At that point, the ChipScope software can download a bitstream to the FPGA to program it with a design including the ILA blocks.

The other approach is to take a presynthesized design, drop ILA cores into that design, then place-and-route, and download the design into the FPGA.

You'll see there is actually a JTAG control block in the FPGA that interfaces with the logic analyzer blocks. Data is pulled out by this control block through the JTAG, back to the PC, and then presented on the ChipScope interface.

|                                      | Setup Waveform Windo         | w Mole                                                       |                            |                    |             |               | <u>_ 8 × </u> |

|--------------------------------------|------------------------------|--------------------------------------------------------------|----------------------------|--------------------|-------------|---------------|---------------|

|                                      |                              | m nep                                                        |                            |                    |             |               |               |

| Project agilent_afk_board_s          | Tripper Sett Faulteden       | Unit:1 ILA/ATC                                               |                            |                    |             |               |               |

| B-C Device 0<br>B-C Unit 0 ILA       | Match Unit                   | Function                                                     | Va                         | lue                | Radix       | Counter       |               |

| Trigger Setup                        | B-M0:SDRAM                   |                                                              |                            | X_0000_0000_0000   | Bin         | at least once |               |

|                                      | -ip_SDR_ad[8]                |                                                              |                            | ×                  |             |               |               |

| Bus Plot                             | -ip_SDR_ad[7]                |                                                              |                            | ×                  |             |               | _             |

| Critte LAATC                         | -ip_SDR_ad[6]                |                                                              |                            | ×                  | ·           |               |               |

| - Waveform                           | ip_SDR_ad(5)<br>ip_SDR_ad(4) |                                                              |                            | x                  | -           |               |               |

| Listing                              | ip_SDR_ad[3]                 |                                                              |                            | X                  |             |               |               |

|                                      | -ip_SDR_ad[2]                |                                                              |                            | X                  | d           |               |               |

|                                      | -ip_SDR_ad[1]                |                                                              |                            | х                  |             |               |               |

|                                      | ip_SDR_ad[0]                 |                                                              |                            | ×                  |             |               |               |

| 4 D                                  | -ip_SDR_web                  |                                                              |                            | 0                  |             |               |               |

| Device:0 Unit1 ILA/ATC               | ip_SDR_casb                  | I                                                            |                            |                    | 4 1         |               |               |

| Data Signals and Buses               | Add Active                   | Add Active Trigger Condition Name Trigger Condition Equation |                            |                    |             |               |               |

| 8-SDRAM                              | 1001                         | T                                                            | riggerCondition0           |                    | MŰ          |               |               |

| E TRIG_IN                            | Type: One Window.            | Depth: 65536                                                 | <ul> <li>Positi</li> </ul> | on: 16000 🕅        | 7 Timestamp |               |               |

|                                      | Waveform - Device:0          | MALL IL & /ATC                                               |                            |                    |             |               | -IOX          |

|                                      |                              | 0 ns 600                                                     | ns 619 ns 647 n            | s 666 ms 684 ms    | 703 ns      |               | 1 ms          |

|                                      |                              |                                                              |                            |                    |             |               |               |

|                                      |                              | 0 0                                                          |                            |                    |             |               | î             |

|                                      |                              | 1 1                                                          |                            |                    |             |               |               |

|                                      |                              | 1 1                                                          |                            |                    |             |               |               |

|                                      | -ip_SDR_web                  | 1 1                                                          |                            |                    |             |               |               |

|                                      |                              | 0000                                                         | 000                        | X 003 X            |             | 000           | ¥             |

|                                      |                              | 2228                                                         |                            |                    |             |               |               |

|                                      |                              |                                                              | X: -320006 ns              | () 0: -320006 ns   | < ▶ △(X-4   | 0):0          |               |

| INFO - Device 0 Unit 1: Sample Buffe | ris full                     |                                                              |                            |                    |             |               |               |

| Parse Trace Data                     |                              |                                                              |                            |                    |             | 04            | ONE           |

|                                      |                              |                                                              | and alle                   | ⊾∉ <b>⊨⊘⊘⊗⊽0</b> ≋ |             |               |               |

| 🏨 Start 🛛 😭 🏭 🖾 🕐                    |                              |                                                              |                            |                    |             |               |               |

Here's a view of the ChipScope Pro interface in its logic analyzer screen.

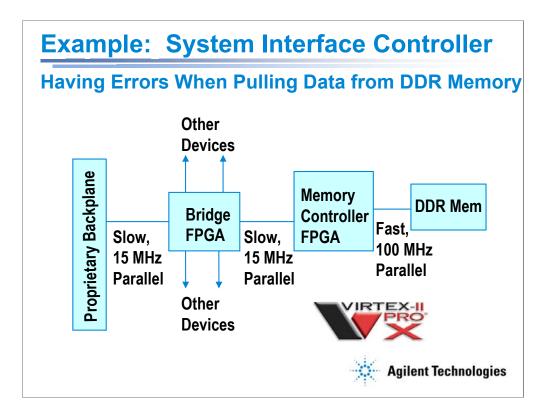

One engineering example involves a case where a system interface controller was experiencing errors when a 15 MHz proprietary backplane tried to read DDR memory via a couple of FPGAs.

The first FPGA really served as a bridge allowing the selection of multiple devices, one being the DDR memory. The second FPGA served as a DDR memory controller and interface between the 100 MHz DDR and the 15 MHz system bus.

Both FPGAs were from the Xilinx Virtex II family.

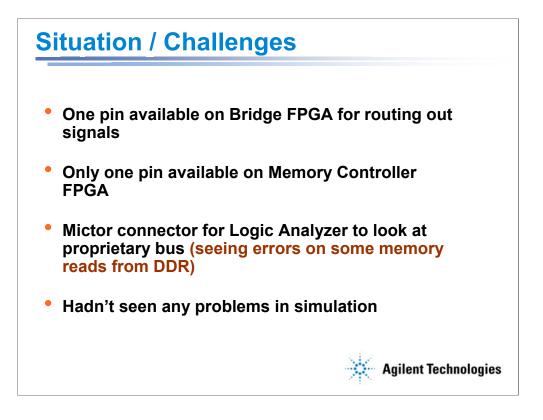

The designer had some tough constraints to work with. First there was only one pin available on the bridge FPGA for routing out internal nodes, and only one pin on the memory controller FPGA. The designer had placed a Mictor connector on its board to be able to look at a proprietary bus with the logic analyzer.

There were errors on some memory reads from DDR, but no errors had been seen in simulation

Given that there was only one FPGA debug pin per FPGA the designer felts he would need to use integrated logic analyzer cores in the FPGAs. He planned to monitor the back plane with logic analyzer, and his hope was that he'd see the source of the problem either by looking at the internal FPGA activity or the external bus activity.

That was hopeful thinking, but the independent ILA core and logic analyzer views did not reveal what the root cause of the problem was. One problem was that the ILA core approach could only have a simple trigger set for them.

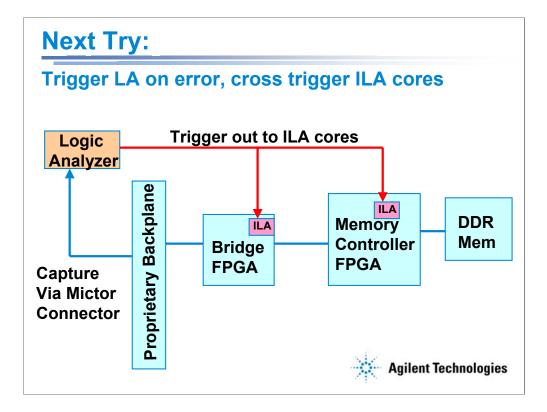

So this was going to take a more complex approach for debug. The designer decided to trigger the logic analyzer when he saw an error on the proprietary back plane, but then trigger the integrated logic analyzer blocks on the inside each of the FPGA case. The goal was to try and understand exactly what was happening inside the FPGAs at the point when the error occurred, and to possibly have to look back in time for the sequence of steps that led up to the visible error seen out on the back plane. Part of the challenge was that it was a multiplexed Address/Data bus on the backplane, and a logic analyzer was necessary to de-multiplex that bus so that you could then trigger on it.

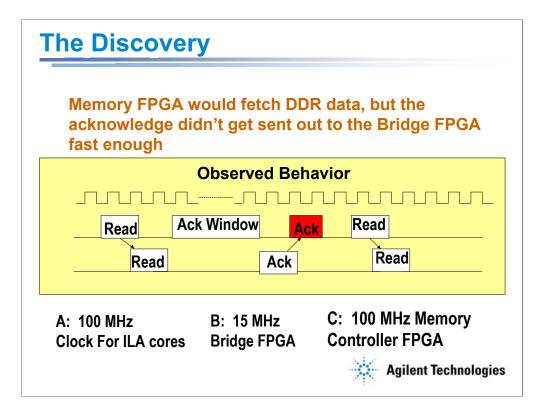

Well that was the right approach. Cross triggering from the back plane condition to the logic analyzer blocks inside the FPGA did in fact uncovered the root cause of the failure. What was happening was when the bridge FPGA requested a read, the memory controller FPGA did a read from 100 MHz DDR memory. But then the 15 MHz bridge FPGA needed to receive an acknowledge signal within a certain time. By looking inside the FPGAs, it became obvious that the acknowledge was coming outside that time window. So this was a timing error, but it didn't deal with set up and hold types of timing problems surrounding the clock edge. This was a timing error that dealt with a sequencing of events between two time domains.

The designer saw the acknowledge problem with the ILA block inside the Bridge FPGA. When looking just at the memory controller FPGA initially without the cross-trigger from the logic analyzer, he could see good data was making it out of the memory FPGA. It was only with a cross trigger, and an ability to see inside the bridge FPGA at the precise time that error occurred on the backplane, that he could catch the acknowledge timing problem.

So the designer had to pull 130 nanoseconds of pipeline stages out of the second FPGA in order to pull this acknowledge signal back in.

It was important to be able to cross trigger from a symptom of the problem with an external logic analyzer, to the ILA blocks inside the FPGAs, in order to see the root cause of the failure.

In this example, by clocking the ILAs from the 100 MHz DDR clock, there was good timing resolution to see the latency problem on the 15 MHz FPGA. ChipScope ILAs D. if asynchronous capture, but it almost served as a timing analyzer on the slower bus.

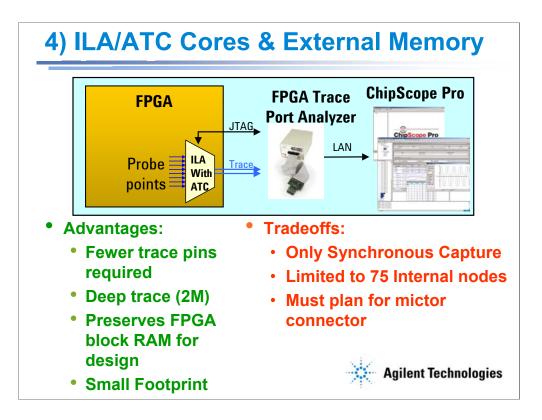

The fourth way of viewing internal nodes in an FPGA is a solution that involves new ILA cores Xilinx coupled with an Agilent trace core (ATC) and an Agilent FPGA Trace Port Analyzer (TPA).

Here, internal nodes are time division multiplexed out to external memory in the TPA. This approach has a number of advantages. The first can be fewer pins as well as up to 2-Meg deep memory, and that memory doesn't draw on FPGA resources. Some of the tradeoffs are similar to the those we saw with the basic ILA approach.

Let's look more closely at the ILA /ATC option.

| gilent Trace C                                             |                                      |    |    |    |                      |  |

|------------------------------------------------------------|--------------------------------------|----|----|----|----------------------|--|

|                                                            |                                      |    |    |    | FPGA<br>pins<br>/ith |  |

| Maximum Internal FPGA<br>Clock Domain Frequency            |                                      |    |    |    |                      |  |

| & Trace Depth*                                             | Available # of Internal Probe Points |    |    |    |                      |  |

| up to 50 MHz with 500K states                              | 11                                   | 27 | 43 | 59 | 75                   |  |

| up to 100 MHz with 1M states                               | 5                                    | 13 | 21 | 29 | 37                   |  |

| up to 200 Mhz with 2M states                               | 3                                    | 7  | 11 | 15 | 19                   |  |

| Required number of FPGA pins                               | 4                                    | 8  | 12 | 16 | 20                   |  |

| NOTE: USER MUST SUPPLY CLOCK FOR TRACE. Agilent Technologi |                                      |    |    |    |                      |  |

Time division multiplexing via the Agilent Trace Core can be very advantageous to reduce pin count. For example, 75 signals running at 50 MHz can be 4:1 TDM'd down to only 20 pins while still giving full visibility to those signals.

Some details follow:

ATC comes in multiple pre-defined configurations depending on the clock speed of the internal circuit to be measured. ATC's TDM is based on the assumption that most FPGA circuits run at a fraction of the speed that the I/O pins are capable of (200 MHz single-ended).

For circuits up to 50 Mhz, this allows Agilent to use a 4:1 time-division MUX and monitor up to 75 probe points simultaneously at a memory depth of 256K states(samples). One channel is used for the clock and as MUXing ratios increase, some of the TPA storage resources are used for sync pulses so when the data is diplayed, triggering and packet information can be unraveled by ChipScope. For circuits running at >50 MHz to 100 MHz, one can use a 2:1 MUX.

#### Agenda

So it's been important to look inside FPGAs for general debug, but it's also very important to look at the FPGA boundary and at other locations in a system at the board level.

When trying to look at FPGA boundary signals or other signals in an overall system, planning for connecting in-circuit debug tools is important. In the last months, the options for such connections have greatly increased.

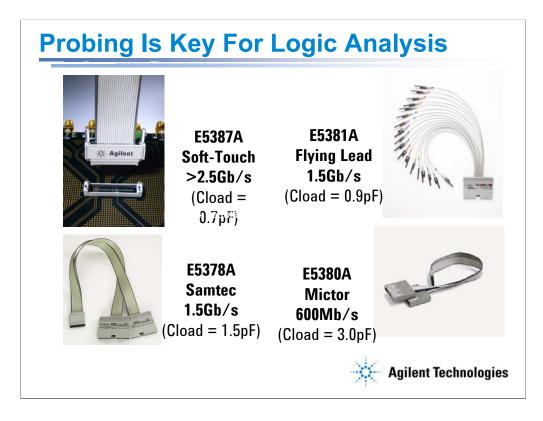

The evolution of Logic Analyzer Probes has given the user the following

-Lower Capacitive Loading

-Higher Resonant Frequency of the Probe Load

-Higher Bandwidth Probes

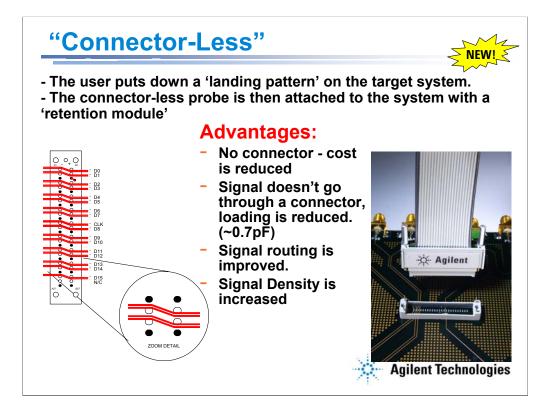

One important, new category of logic analyzer probes is called "Connector-Less" probing. This is the newest technology in logic analyzer probing and presents some of the most attractive options to the end user.

The concept of a connector- less probe is that the user only puts down landing pads on his PCB. Traces are routed to or through the pads. A retention module is used to align the probe tip with the pads and provide mechanical stability. The logic analyzer probe is then attached to the board with the assistance of the retention module and makes contact with the pads on the board.

The advantages of connector- less probing are that since the signals do not travel through a connector to get to the logic analyzer probe tip, there is less capacitive loading on the target. For example, the E5378A probe discussed earlier had an equivalent lumped capacitance of 1.5pF. Connectorless probes are on the order of 0.7pF, a 2x improvement. Also attractive about this new technology is that the user does not need to load connectors onto the target PCB, reducing the cost of the final assembly. Finally, improvements have been made to the rout e-ability of connector- less probes. The user can now easily route directly through the probe pads without making layer changes. Since the capacitance is so low and there is no connector, the logic analyzer footprint can be left in the design on the final release of the PCB without any electrical degradation to system performance.

## Probing is Also Key For Scopes

| V | 500 MHz BW<br>passive probes                              | Clock rates<br>up to around<br>100 MHz | Edge speeds<br>as fast as 2<br>nsec   |

|---|-----------------------------------------------------------|----------------------------------------|---------------------------------------|

|   | 1.5 GHz BW<br>1156A active<br>probes (1 GHz<br>system BW) | Clock rates<br>up to around<br>200 MHz | Edge speeds<br>as fast as 1<br>ns     |

|   | 3.5, 5 & 7 GHz<br>BW 1130<br>InfinMax active<br>probes    | Clock rates<br>up to<br>multiple GHz   | Edge speeds<br>as fast as<br>100 psec |

|   |                                                           | *                                      | Agilent Technologies                  |

An important part of debugging FPGA-based systems is the ability to make oscilloscope measurements both at the FPGA boundary and at other points in the system. Passive probes have their place, but at the faster clock rates and edge speeds scope bandwidths of 1 GHz or better become necessary. For the 1 GHz Infiniium scopes, the 1156A active probes are the right choice to maintain a full 1 GHz system bandwidth for single-ended measurements. A wide range of connection accessories with documented performance give lots of options for how to attach to various points in the system. Soon there will be new differential active probes to maintain full system bandwidth as well.

For the very fast signals, the 54850 series of Infiniium scopes are a best fit. For these scopes, the InfiniMax single-ended and differential probes and various high bandwidth connection accessories offer unmatched performance.

Calculations for limits in edge speeds are based on system bandwidths necessary for around a 5% rise time measurement error. The 500 MHz and 1 GHz scope models assumed a gaussian scope frequency response, and the very high bandwidth scope models (> 1 GHz bandwidth) assumed a flat scope frequency response. Designers may be comfortable with higher errors than 5%, especially for timing measurements, which would extend the use range.

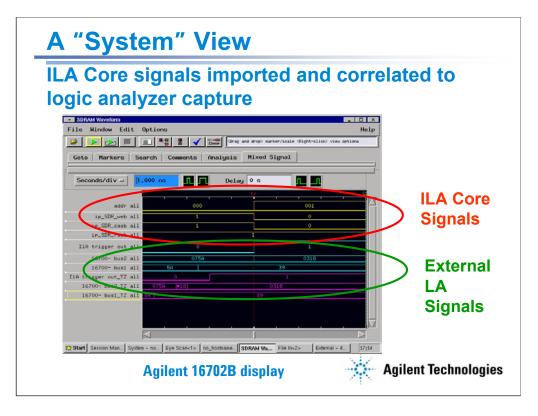

When making measurements in the system, it can be helpful to see both the internal FPGA signals and other system signals. Earlier we saw a view of SDRAM signals internal to a Xilinx Virtex II Pro FPGA. What about trying to view other system signals in context with those internal FPGA signals?

Xilinx and Agilent have worked together to make this easy. By dedicating one pin for a common debug signal, Xilinx ChipScope Pro can export internal FPGA signals by LAN to Agilent system logic analyzers. Here's a logic analyzer view of ChipScope data time correlated the logic analyzer captured data.

What about an example of looking at the boundary of an FPGA?

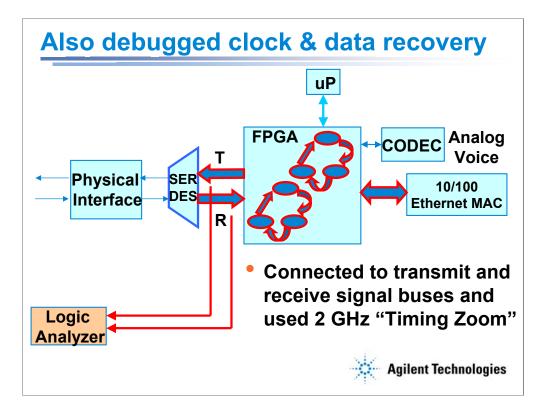

If we look back to that earlier fiber to the home ATM network example, there was another interesting debug situation on this same design, that involved the debug of the clock and data recovery circuits on the front end. These were measurements taken outside the FPGA on its boundary, where the parallel transmit and receive buses interfaced with the FPGA.

They were having a failure, and trying to see the conditions surrounding this error. They put the transmitter on one logic analyzer machine and the receiver on the other, and gathered a deep trace to begin looking for the nature of the problem. They ended up using a single logic analyzer machine and its 2 GHz Timing Zoom capture to observe clock phase with respect to data and the conditions where errors were occurring.

A few takeaways from this example:

The designer had a need to look at signals outside the FPGA that needed to meet FPGA input specifications, likes the clock and data recovery circuit signals, with high-speed 2 gigahertz timing.

## Agenda

So we've looked at several customer debug examples and considered some of the options surrounding basic debug. What can we learn from this?

First, we've seen how embedded logic analyzer cores can be very helpful for visibility into FPGAs. We've also seen that external logic analyzers or scopes can be helpful too, given deep memory and the ability to do careful timing analysis. In fact, both approaches have their place and can be used together. Given that, it is still wise to dedicate some pins for this external trace.

So for starters, plan so that you have options for ILA capability, with either a BERG connector for basic capture in Block RAM, or with a Mictor connector for the new off-chip approach with a Trace Port Analyzer.

Here are some possible ideas about the number of debug pins you might need. It was clear, from the examples we've discussed, that it was often critical to be able to have enough pins to see internal state machines, and to see datapaths. Then take advantage of the ways additional visibility is possible with the ILA cores.

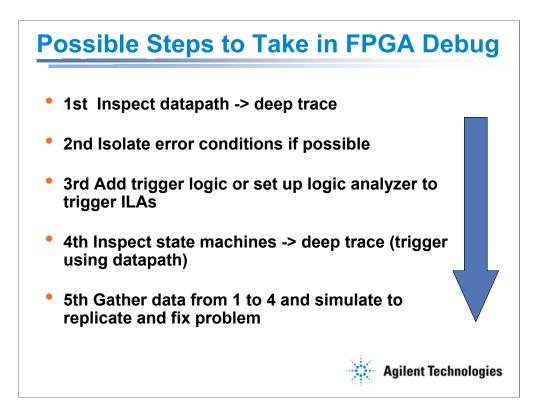

Looking at a variety of debug situations, a common theme seemed to form in the way people discovered fixes to their problems. Many times, designers saw a symptom of a problem on a bus, figured out how to isolate that symptom, and then defined a trigger so that they could look internally to the FPGA to see state machine activity. With that kind of visibility, they could form a hypothesis to the problem and simulate it. Then the fix would become obvious.

## Agenda

So what about approaches when dealing with high speed I/O debug and characterization?

First, there are a number of options for looking at passive interconnect to understand transmission line characteristics. These vary from sampling oscilloscope based solutions like Time Domain Reflectometry, or TDR, to Vector Network Analyzer based solutions. There are also simulation tools very useful to understand high frequency analog effects to fast digital signals.

To understand whether a high-speed I/O is working properly, you certainly can't only look at the passive interconnect. That's where a wide variety of measurements come into play to look at fast I/O signals and the transfer of data in a system.

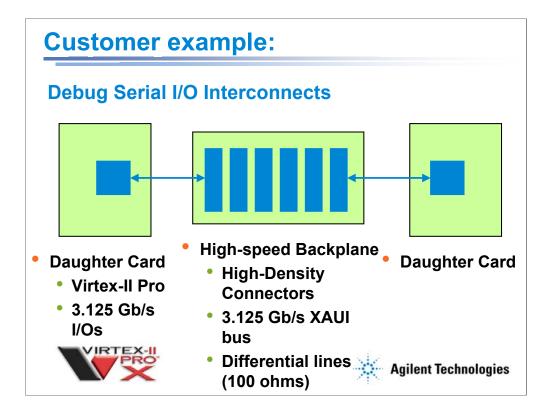

Our final example crosses over from general debug over into high speed I/O debug and characterization. Here a company was designing the backplane structure for line cards in a router. It was going to run at 3.125 Gb/s XAUI.

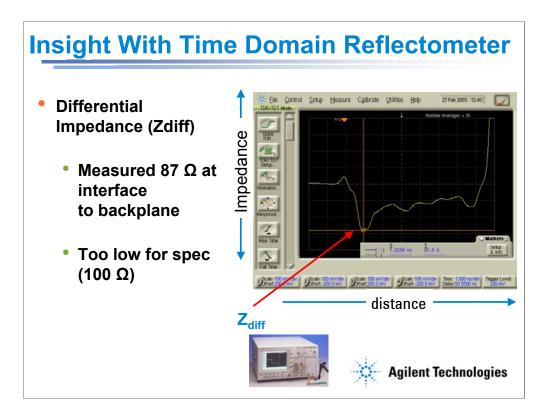

It was necessary to characterize the performance of the transmission line paths from the FPGA I/O output to the FPGA input on a second daughter card. A spec had to be met for impedance and crosstalk.

The TDR showed where the impedance was too low, and pointed to the location where capacitance needed to be designed out of a transition from the daughter board PC board trace out to a connector.

The measurements pointed to the need for a better termination at the far end.

New measurements are now available with the advent of high bandwidth real-time scopes and new technology differential active probes. Some of the planning for this can include routing some key signals on the surface so if it is necessary, the LPI layer can be scratched back to expose a differential pair, or the LPI layer can be omitted from an area intended for probing.

## **Higher Bandwidth Connection Solutions**

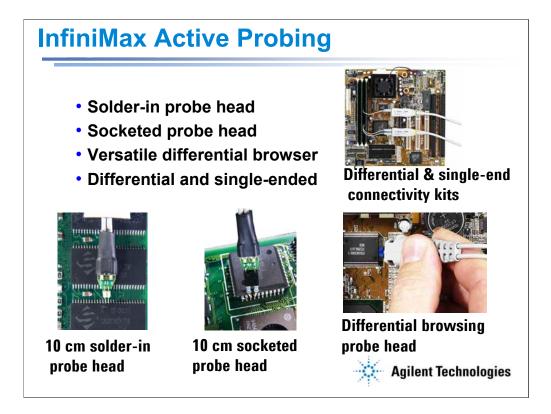

Use models for the InfiniiMax active probe system are similar to traditional active probes, including "browsing" connections, 10cm solder-in connections, and 10cm socketed connections. In addition, the InfiniiMax probe system includes both single-ended and differential measurement use models. The big difference between the InfiniiMax probe system and traditional active probe systems is probe system bandwidth. Even with long connection use models, there is no bandwidth loss penalty.

For high-speed I/O on ball-grid array type FPGAs, it is probably not best to place vias under the FPGA. It turns out, if you do, you don't gain too much for probing since there is still as much as a 14 mm trace from the package to the substrate. You'll probably want to use a double termination (source and receiver), and route key signals to the surface so you can do mid-bus probing. One approach is to simply design a small area where those traces are not coated with LPI (insulated coating on top of board) for easy differential probe access. Alternatively, one can scratch off the LPI in area desired for probing.

Sometimes it's best to probe back at a transmitter location, even though the receiver is inside the FPGA at the substrate point.

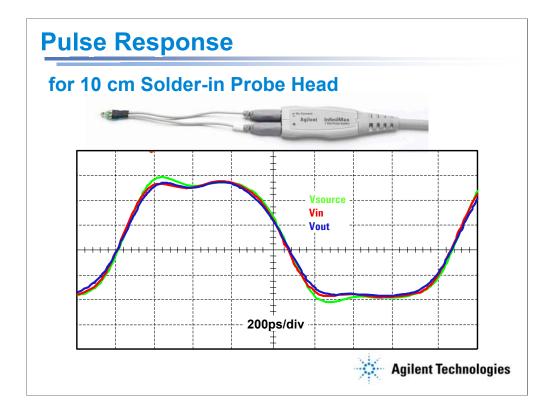

## Pulse Response for 10cm solder-in probe heads – 1.2GHz Clock, 100ps Risetime

These are the same waveforms shown in the previous slide for the 10cm solder-in probe head with all of the waveforms overlaid on top of one another. This is as good as it gets! No other scope and probe combination can duplicate these results. From any vendor.

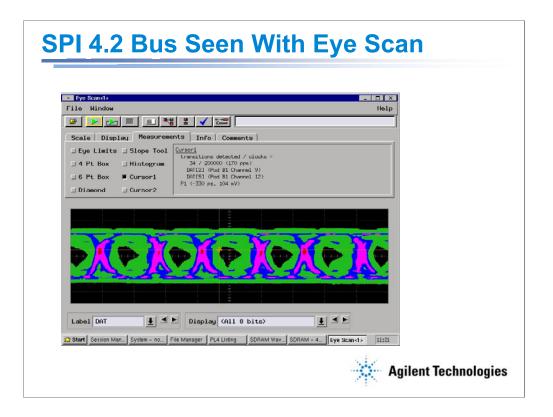

Designers also face signal integrity validation on fast parallel buses, such as 622 MHz SPI 4.2 signals. Now there is a new approach to identifying problems. It's with a logic analyzer and called Eye Scan.

Eye Scan is a third "mode" in a logic analyzer beyond "State" or "Timing" modes. With Eye Scan, the analyzer threshold is not just set to a "1 - 0" level, but rather is varied over a range of levels. For each level, the analyzer also adjust the time point of observation before and after trigger, and then counts the number of transitions it sees through the threshold.

The result is that over many clocks, an eye diagram is built up with multiple GHz analog bandwidth, and looking at many signals.

Here, with a cursor, we could just touch the left had side of the eye opening, and see exactly "which" bits are closing off the eye.

This can point a designer immediately to problems on specific bits such as jitter, noise, crosstalk, or other signal integrity issues. Then a high bandwidth scope and active probe can be used to look more closely.

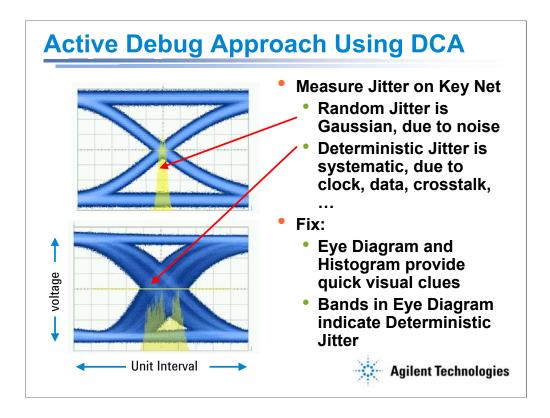

Earlier we used TDR and crosstalk measurements to look at a passive interconnect. It is also important to make some measurements on signals through the backplane and look at jitter. It is possible to separate out the random jitter and deterministic jitter with software tools. Here is an example where it is obvious that there is data dependent, deterministic jitter that could pose a problem.

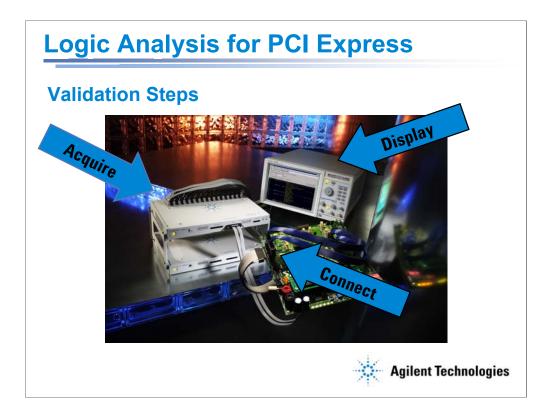

With some of the fastest serial I/Os, such as PCI Express, dedicated solutions are necessary to validate the bus or reveal problems. An example is the front end probe required to de-multiplex the fast PCI Express signal into slower, parallel signals that the logic analyzer can consume. Such a probe includes sophisticated triggering capabilities as well, thus reserving trigger resources inside the logic analyzer frame and acquisition module.

This solution uses the SoftTouch technology to do either mid-bus probing to a field of pads or an attachment into a PCI Express slot.

There were a number of important takeaways for I/O characterization..

Takeaways continued.

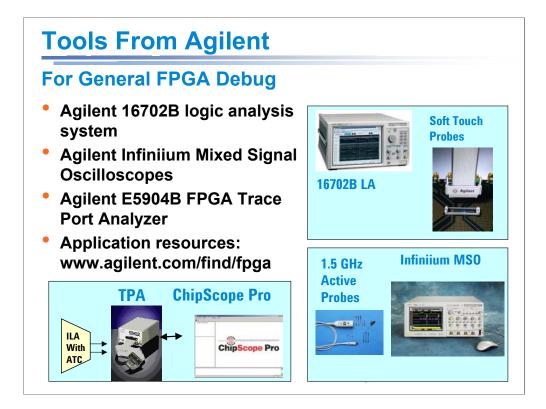

When it comes to basic FPGA system debug, Agilent provides a variety of tools to help the designer of an FPGA based system, from the new Trace Port Analyzer to see internal nodes, to Mixed Signal Oscilloscopes for basic viewing of system activity, to logic analyzers with sophisticated triggering and data interpretation to point the designer to the root cause of their problems.

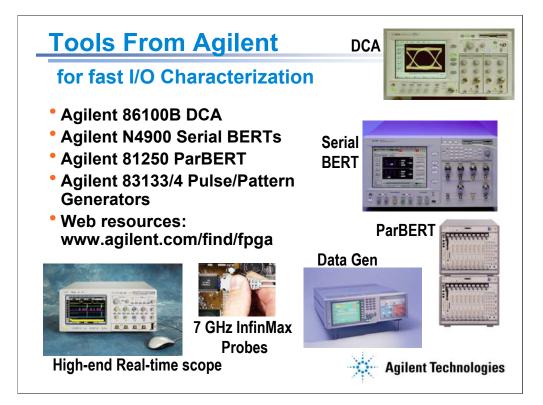

When it comes to systems with fast I/Os, Agilent provides a variety of tools to help the designer of an FPGA based system, from the CSA to parallel bit error rate testers.